**Research article**

Available online www.ijsrr.org ISSN: 2279–0543

# International Journal of Scientific Research and Reviews

# Cascaded H-Bridge Multilevel Inverter Based On Multidimensional Modulation Technique FED PMSM Drive

## A.Subramanian<sup>1\*</sup>and G. Ajithkumar<sup>2</sup>

<sup>1</sup>Professor, Department of EEE, IFET college of Engineering, Villupuram, Tamilnadu. India. <sup>1</sup>annamalaniasmani@gmail.com. <sup>2</sup>UG scholar<sup>•</sup> Department of EEE, IFET college of Engineering, Villupuram, Tamilnadu. India. <sup>2</sup>gakifeteee@gmail.com

## ABSTRACT

This work proposes a multidimensional modulation (MDM) strategy based cascaded Hbridge multilevel inverter (CHBMLI). Various control techniques are employed in manipulating high energy output voltage from CHBMLI. Which is highly suitable for the variable speed drives that are naturally nonlinear in character. The proposed CHBMLI uses reduced number of switching devices that on the whole of the circuit operation minimizes the losses and hence improves the efficiency and performance. Multidimensional modulation control method accomplishes the output voltage in a controlled manner of improved THD. The performance of the MDM-CHBMLI is simulated in MATLAB/Simulink environment and the results are verified with the experimental implementation. The output of the MDM-CHBMLI assures its suitability on the PMSM drive operation.

**KEYWORDS:**Multidimensional modulation, multilevel inverter, Cascaded H-bridge topology, High energy voltage, Harmonics reduction.

#### \*Corresponding Author

#### A.Subramanian

Professor, Department of EEE,

IFET college of Engineering, Villupuram,

Tamilnadu. India.

E Mail - annamalaniasmani@gmail.com

#### I. INTRODUCTION

In a Multilevel inverter and its other cascaded topologies control strategy is very important on producing output voltage close to sinusoidal wave <sup>1.</sup> Multilevel direct power control (ML-DPC) is a method which can be considered as a generalized method on any level of MLI to produce gating pulses. MLIs are prominent on producing high energy output voltage to drive the ASD drives, grid connected power converters etc.<sup>2, 3,4,13</sup>. Asymmetric cascaded H- Bridge MLI has been selected to drive the PMSM ASD drive which has given improved performance comparatively over other converts implementation in operation <sup>5</sup>. Improving the efficiency of MLI is very essential while adopting them on driving the high power requiring industrial loads; by eliminating selective low level harmonics the efficiency can be increased. The switching losses in a MLI is limited <sup>7</sup> by reducing the number of switches and using the voltage limited capacitors. Cascading two and more number of Hbridge inverters to increase the output voltage and reducing the harmonics is possible<sup>8</sup>. Different configuration and topologies are developed to fulfil the load requirement, <sup>9</sup> diode assisted boost NW based CHB-MLI uses low power rated switches and be used for reactive power compensation. It also uses less number of switching power devices isolated from DC sources. This topology makes the current stresses across all switching devices equal. Induction motors are simple, efficient and low budget drive that are normally accommodated in industries and domestic loads <sup>10</sup>. The CHBMLI adopted induction drives are brought into market based on its improved performance.Multidimensionalmodulation technique<sup>11</sup> was applied in CHBMLI configuration towards increasing the efficiency and improving the output operation  $^{12}$ ; 15 level inverter topology has been simulated by the author towards raising the efficiency of the MLI. Optimization algorithms are adopted in the MLI topologies to reduce the harmonics. Section 1 describes the various work carried out by the researches on CHBMLI planning on improving the efficiency and performance, section 2 details the CHBMLI and section 3 explains the operations of MLI and section 4 gives the conclusion of the work.

#### **II. CASCADED MULTILEVEL INVERTER**

In a short period MLI based inverters are finding many application on grid connected converter operation, ASD drives and industrial applications [13]. A CHB multilevel inverter motor drive has been implemented to drive the PMSM motor. A MLI generally constructed with many cells of a capacitor connected with active power switches for conversion. Each cell will be connected with a DC source of variable voltage magnitude. The DC sources may be solar PV cell, fuel cell and battery. The output from CHBMLI will be the sum of voltage from different cells. This nature of

operation reduces the stress on the switches and eliminate the harmonics content. The output voltage from a cell CHBMLI will be,

$$Vo(t) = V_0(t) + Vo_2(t) \dots Vo_2 + V_{ON}(t)(1)$$

$$Vo(t) = \Sigma(\mu j - 1)V_{dc}(j)\mu j=0, 1, 2...(2)$$

In a symmetric MLI all the  $V_{dc}$  voltage levels are same for a n level MLI and the value of n=1+2N and the

$$V_0 max(t) = NVdc$$

(3)

The symmetric MLIs are suitable on providing many output voltages. It is proposed to select input sources based on geometric progression with a factor of 2 or 3. For an 'n' level inverter the following output voltages can be achieved.

$$n=2^{N+1}-1 \quad \text{ if } v_{dc} \ j=2j-1 V_{dc} \ j=1,\,2,\,3\ldots N \ \ (4)$$

$$n=3^n(5)$$

The maximum output voltage of n cascaded multilevel inverter is,

$$V_{o}max = = \sum_{n=1}^{\infty} Vdc(6)$$

$V_{o}max = (2^{n}-1) Vdc \text{ if } Vdc, j=2^{i}V_{dc}(7)$  j=1, 2, 3....n  $V_{o}max = \frac{3^{n}-1}{2} + Vdcif Vdc, j=3^{i}-V_{dc}(8)$  j=1, 2, 3....n

In general the number of DC source and switches involving is a symmetrical and asymmetrical structure of MLI in shown in table 1.

| H-bridge i voltage V <sub>i</sub> | H-bridge i state H <sub>i</sub> | Gate driver signals                       |

|-----------------------------------|---------------------------------|-------------------------------------------|

| -V <sub>Ci</sub>                  | 0                               | S <sub>i1</sub> =1 and S <sub>i2</sub> =0 |

| 0                                 | 1                               | S <sub>i1</sub> =0 and S <sub>i2</sub> =0 |

| 0                                 | 1                               | S <sub>i1</sub> =1 and S <sub>i2</sub> =1 |

| V <sub>Ci</sub>                   | 2                               | S <sub>i1</sub> =0 and S <sub>i2</sub> =1 |

Table 1: "Gate driver signals depending on H-bridge i state"

#### **III. MULTIDIMENSIONAL MODULATION TECHNIQUE**

Modulation techniques are adopted in all types of single and multilevel inverters to produce phase voltages. Complication in the generation of pulse signal is increasing as the number of phases increases and number output voltage level increases in the inverter. Many pulse generation techniques are introduced by the researchers and implemented in many real time application. Modulation based PWM generators were introduced in many MLIs. Phase shift, level shift and carrier modulated PWM techniques were applied in real time. Multidimensional modulation is a recently developed method to face the problems on developing multilevel output voltage (or) stepped waveform. In a multinational n-level MLI using MDM n-1 carrier waves are placed with a phase shift among the adjacent waves,  $\theta$ =360/ (n-1). These pulse signals are arranged on turning the pulse generator ON. The pulse voltage v<sub>ref</sub> is given by,

$$\mathbf{V}_{\mathrm{xy}} = \delta_1 + \delta_2 \tag{9}$$

$\delta_i = \int_0^{Tsw} Vi \ dt \ (10)$

The H-bridge can establish output voltages of -E, zero and +E for the gate pulse applied. In a seven level inverter the phase shift between the adjacent carrier wave is  $\theta = 360/(7-1) = 60^{\circ}$

#### **IV. SIMULATION RESULTS**

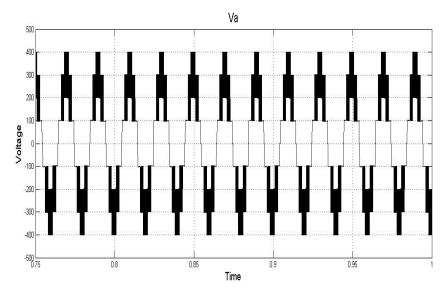

The7-level MLI was simulated on matlab Simulink environment and the output voltage, current and other signal components are obtained. The seven level voltage waveform are shown in fig 4.1

Fig 4.1: Voltage waveform of 7 level inverter

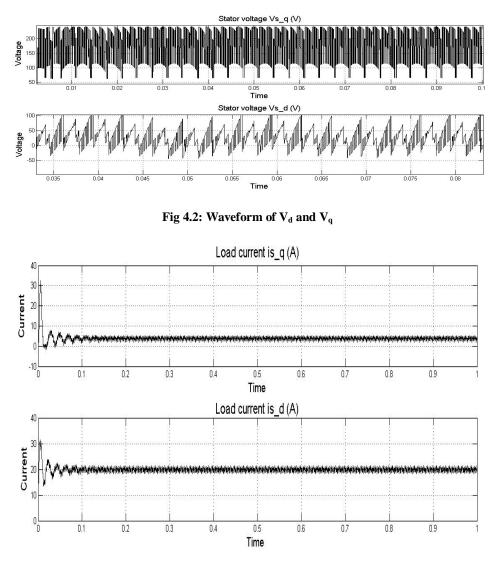

When the PMSM motor is connected, voltage from the MLI gets divided into direct and quadrature axis components as  $V_d$  and  $V_q$ . The value of Vq determines the torque development in the motor. The fig 4.2 shows the  $V_d$  and  $V_q$  voltages of the PMSM motor.

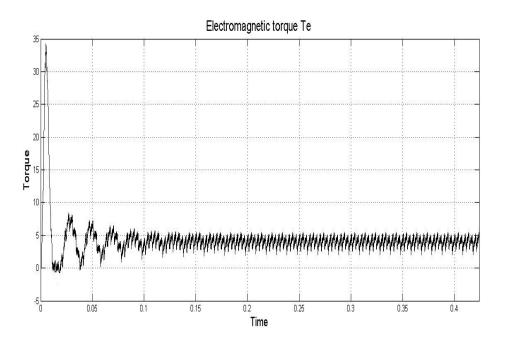

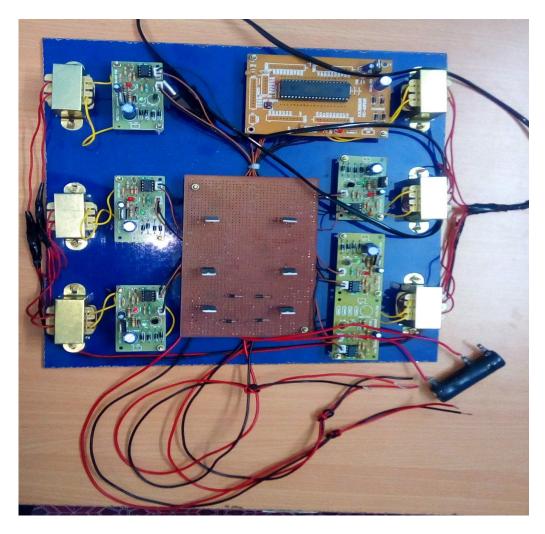

Fig 4.3: Waveform of  $I_d$  and  $I_q$

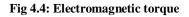

Fig4.3 gives the  $I_d$  and  $I_q$  it's of PMSM motor and the torque developed is shown in fig4.4

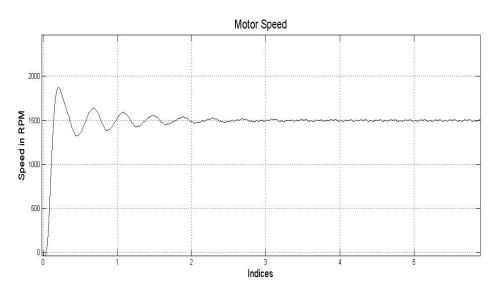

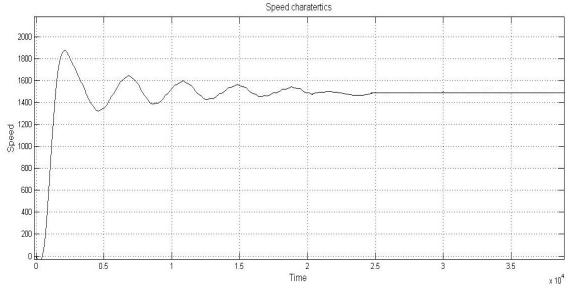

From the graph it is clear that the speed of the PMSM motor is reaching its steady state level after its settling time that is the current is made smooth and constant with shown in fig 4.5

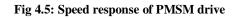

The fig 4.6 shows the prototype model of the 7-level MLI. The output voltage and current are compared with the simulation results.

Fig 4.6 Prototype model of the 7-level MLI

Fig 4.8 Speed response of prototype model

#### **V. CONCLUSION**

Multilevel inverter for 7 level has been simulated using multidimensional modulation strategy and thesimulated results were compared with the hardware output. MDM control technique has developed exact gate pulses and that made the output voltage and current waveform with reduced distortion and harmonics. The PMSM motor direct and quadrature axis voltage and current are divided properly on determining the torque signal. The performance of the PMSM motor has been improved with the use of MLI inverter controlled by MDM technique.

## VI. REFERENCES

[1] Sebastian Rivera, Samir Kouro, Bin Wu, Salvador Alepuz, Mariusz Malinowski, Patricio Cortes, Jose Rodriguez. Multilevel direct power control-A generalized approach for grid-tied multilevel converter applications. IEEE Transactions on power electronics 2014; 29:5592-5604.

[2] Sravan Kumar Thappeta, Ranga J A new cascaded multilevel inverter fed permanent magnet synchronous motor by using sinusoidal pulse width modulation. International Journal of Engineering Research and technology 2013; 2:1513-1520.

[3] Haris M, Pathak M K, PramodAgarwal. Comparison of SPWM multilevel inverter fed PMSM drive with two level inverter fed drive. IEEE international conference on recent advances and innovations in engineering. 2014; 14:9781-9788.

[4] Richapandey, Dubey S P. Multilevel fed permanent magnet synchronous motor drive with constant torque angle control. Advance in electronic and electric engineering. 2013; 3:521-530.

[5] Gobinath k, Mahendran S, Gnanambal I. New cascaded h-bridge multilevel inverter with improved efficiency. Internal national journal of advanced research in electrical, electronics and instrumentation engineering. 2013; 2:1263-1270.

[6] Divya Subramanian, RebiyaRasheed. Nine-level cascaded h-bridge multilevel inverter. 2013; 3:201-205.

[7] Anupriya Jain, shobhna Jain. Harmonics reduction in inverter with different techniques including fuzzy logic controller. International journal of science and research 2015; 4:1819-1822.

[8] ShaliniTahunguriya, Rakesh Kumar A, Deepa T. Multilevel inverter with reduced number of switches and reduction of Harmonics. Middle-east journal of scientific research 2016; 24:184-191.

[9] Bharatiraja C, Aishwarya Ravi, Sanchari Banerjee, AbhishekChakraborty, AniruthAnupam, AksheyMenon. A hybrid cascaded multilevel inverter with diode assisted boosting network. Energy procedia 2017; 117:1024-1031.

[10] Prathana Nagle, Sharma C.S, Manoj Jiani, Phulambrikar. Cascaded H-bridge multilevel inverter fed induction motor drive. International journal of innovative research in electrical, electronic instrumentation 2017; 5: 32-35.

[11] Jose Ignacio leon, Samir kouro, Sergio Vazquez Ramon portillo, leopoldo Garcia franquelo, Juan manuelcarrasco, Jose rodriguez. Multidimensional modulation technique for cascaded multilevel converters. IEEE transaction on industrial electronics 2011; 58:412-420.

[12] Sandihiya M, Meena S, Dr. Mahesh Manivanna Kumar G. Multilevel inverter topology with reduced number of switches. International research journal of engineering and technology 2018; 5:71-74.

[13] Yazhini R, Jagabarsathik M, Dr.Ramani K. Analysis and modelling of new modified multilevel inverter with PMSM applications. International journal of scientific and engineering research 2014; 05:178-182.

[14] AyoubKavousi, behroozvahidi. Application of the bee algorithm for Selective harmonic elimination strategy in multilevel inverters. IEEE Transactions on power electronics. 2012; 27: 1689-1696.